**RESEARCH ARTICLE**

**OPEN ACCESS**

# A BUILT-IN SELF REPAIR ANALYZER FOR WORD-ORIENTED MEMORIES

Kowsalya.S<sup>1</sup>, Somu.K<sup>2</sup>, Saravanakumar.P<sup>3</sup> PG Student, VLSI Design, Department of ECE, Maha Barathi Engineering College, India<sup>1</sup> (Kowsalyakowsalya54807@gmail.com) Professor, Department of ECE, Maha Barathi Engineering College, India<sup>2</sup> (somu.pgp@gmail.com) Assistant Professor, Department of ECE, Maha Barathi Engineering College,India<sup>3</sup> (yasaraa@gmail.com)

#### ABSTRACT

In this project a built-in self repair analyzer with the optimal repair rate for memory arrays with redundancy. The existing techniques used depth first search using a stack and a finite-state machine. The formulation of the circuit allows using the parallel prefix algorithm, it can be configured in various ways to meet area and test time requirements.. The content addressable memory is used to identify the fault address to store in must-repair analyzer. The proposed methods using the bit swapping linear feedback shift register to reduce both the transition and the power consumption, and also using precomputation content addressable memory to reduce the time delay in the must-repair analyzer. It requires only a single test, even in the worst case. By performing the must-repair analysis during the test, it selectively stores fault addresses, and the final analysis to find a solution is performed on the stored fault addresses. The infrastructure is also extended to support various of word-oriented types memories

depth first search, finite-state machine, BIST

#### **1.INTRODUCTION**

(SOC) Today's System-On-Chip environment requires significant changes in testing methodologies for memory arrays. The failure of embedded memories in a SOC is more expensive than that of commodity memories because a relatively large die is wasted. Due to the large die size and the complex fabrication process for combining memories and logic, SOC suffer from yield, necessitating relatively lower vield optimization techniques. At present, the area occupied by the embedded memories takes more than half of the total area of atypical SOC, and the ratio is expected to keep increasing in the future. In addition, the aggressive design rules make the memory arrays prone to defects. A SOC consists of both the hardware and software. The software controlling the microcontroller, microprocessor or DSP cores, peripherals and interfaces. The design flow for a SOC aims to develop this hardware and software in parallel. Therefore, the overall SOC yield is dominated by the memory yield, and optimizing the memory yield plays a crucial role in the SOC environment.

To improve the yield, memory arrays are usually equipped with spare elements, and external testers have been used to test the memory arrays and configure the spare elements. However, in the SOC environment, the overall test time is prohibitively increased if the test response data from the memory arrays are sent to the external testers. On the other

Keywords:

hand, the SOC environment, combined with shrinking technology, allows us more area for onchip test infrastructure at lower cost than before, which makes feasible a variety of built-in self test (BIST) and built-in self-repair (BISR) techniques for reducing the test time, and also it is to test the memory arrays.

#### **1.1 SYSTEM-ON-CHIP**

A system on a chip or system on chip (SOC) is an integrated circuit (IC) that integrates all components of a computer or other electronicsystem into a single chip. It may contain digital, analog, mixed-signal, and often radio-frequency functionsall on a single chip substrate. A typical application is in the area of embedded systems.

The contrast with a microcontroller is one of degree. Microcontrollers typically have under 100 KB of RAM (Random Accessable Memory) (often just a few kilobytes) and often really are single-chip-systems, whereas the term SOC is typically used for more powerful processors, capable of running software such as the desktop versions of Windows and Linux, which need external memory chips (flash, RAM) to be useful, and which are used with various external peripherals.

In short, for larger systems, the term system on a chip is a hyperbole, indicating technical direction more than reality: increasing chip integration to reduce manufacturing costs and to enable smaller systems. Many interesting systems are too complex to fit on just one chip built with a process optimized for just one of the system's tasks. Therefore, the overall SOC yield is dominated by the memory yield, and optimizing the memory yield plays a crucial role in the SOC environment. The defects are thus likely to affect the functionality of the memory arrays rather than that of logic.

When it is not feasible to construct a SOC for a particular application, an alternative is a system in package (SiP) comprising a number of chips in a single package. In large volumes, SOC is believed to

be more cost-effective than SiP since it increases.

## 2.AN ADVANCED BIRA FOR MEMORIES WITH AN OPTIMAL REPAIR RATE AND FAST ANALYSIS SPEED BY USING A BRANCH ANALYZER

As memory capacity and density grow, a corresponding increase in the number of defects decreases the yield and quality of embedded memories for systems-on-chip as well as commodity memories. For embedded memories, built-in redundancy analysis (BIRA) is widely used to solve quality and yield issues by replacing faulty cells with healthy redundant cells.Many BIRA approaches require extra hardware overhead in order to achieve optimal repair rates, or they suffer a loss of repair rate in minimizing the hardware overhead. An innovative BIRA approach is proposed to achieve optimal repair rates, lower area overhead, and increase analysis speed. The proposed BIRA minimizes area overhead by eliminating some storage coverage for only must-repair faulty information. The defective cells detected by the BIST circuit are replaced by the cells of the spare SRAM.

In the case of embedded memories for systems-on-a-chip (SOC), built-in redundancy analysis (BIRA) is widely used as a solution to solve quality and yield issues by replacing faulty cells with extra good cells. The proposed BIRA analyzes redundancies quickly and efficiently by evaluating all nodes of a branch in parallel with a new analyzer which is simple and easy-toimplement. Experimental results show that the proposed BIRA allows for a much faster analysis speed than that of the state-of-the-art BIRA, as well as the optimal repair rate.

#### **3.MUST REPAIR ANALYZER**

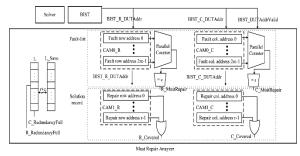

The Must Repair Analyzer(MRA)circuit diagram is as shown in Fig.3.1. It consists of a pair ofCAMs for fault addresses, called the fault-list, and a pair ofCAMs for a repair solution, called the solution record. The memory is repaired during testing by storing faulty addresses in registers. These addresses can be streamed out after test completion. Furthermore, the application can be started immediately after the memory BIST passes.In the fault-list, each CAM has one extra valid bit for eachword, and the valid bits are initialized to "0" in the beginning.Since the CAMs assert "1" at the valid bit position for write andmatch operation, only written entries can be matched. Duringthe test, if the BIST engine detects a fault, it sends the faultaddress to the MRA on the fly through BIST\_R\_DUTAddr andBIST\_C\_DUTAddr, continues the test. The row (column)fault address is compared against row (column) CAM entries.

Fig3.1 Must Repair Analyzer

And the number of matched entries is efficiently counted by a parallel counter. If the number of the matched entriesequals in the row (column) CAM, the row (column) indicatedby the fault address satisfies the must-repair condition andR\_MustRepair (C\_MustRepair) signal is asserted. If the faultaddress triggers neither the row nor column must-repair condition,MRA writes the row and column address in the row and column CAMs, respectively. Due to Corollary 2, we can limitthe size of the fault-list as 2, and if the overflow of the fault-listoccurs, the memory array can be determined as unrepeatable, and the test can be terminated early.If a particular row or column is identified as must-repair, therow or column address must be part of the solution. Thus theMRA writes the row or column address in the solution record. The L registers are used as valid bits for the solution record in fig 3.1.

Since a must-repairrow and a must-repair column can be identified by a faultat the same time, the MRA should be able to write a pair of rowand column addresses simultaneously. Once a row or columnaddress is stored as part of solution by the must-repair condition, then all solution candidates considered by the SOLVER include the address, and faults on the address do not affect the final analysis any more. Therefore, such faults do not need to be stored, and we can collect all necessary information for the final analysis during a single test. Once the test is completed (thus the must-repair analysis is done), BIST\_Done signal is asserted and the final analysis is started. In the final analysis, the SOLVER module controls the MRA.

#### 3.1SOLVER

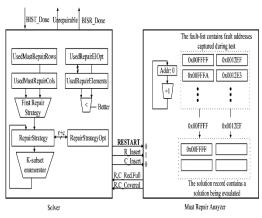

The SOLVER has a register to store the cost of the current repair strategy, orUsed Repair Elements. The SOLVER has a register to store the cost of the current repair strategy, or Used Repair Elements. The SOLVER also has registers to store the repair strategy with minimum cost so far and the minimum cost, or Repair Strategy Opt and Used Repair ElOpt. The current cost is compared against the minimum cost so far, which generates the Better signal. If the Better signal goes down duringthe evaluation of the current repair strategy, the SOLVER immediatelyasserts the RESTART signal and moves on to the nextrepair strategy. If the Better signal stays at "1" until the end of the evaluation, the SOLVER saves the current repair strategy and its cost. Since the SOLVER continues to search for a better solution even after finding a solution, the MRA may not have the optimal solution after the last repair strategy is evaluated. The Must-Repair Analysis repairs rows and columns for which there is no other choice.

Fig 3.2 Solver Circuit

To reduce area, we have stored the optimal repair strategy instead of the optimal solution. If the solution is directly stored, the size of the solution record should be doubled. Thus we need to recover the solution from the repair strategy, and the SOLVER goes into recovery phase. Since the SOLVER continues to search for a better solution even after finding a solution, the MRA may not have the optimal solution after the last repair strategy is evaluated. The solver and MRA circuit operation on shown in Fig 3.2, the MRA gives the fault address to solver. In the recovery phase, the optimal repair strategy, stored in the Repair Strategy Opt, goes into the Repair Strategy register and the strategy is evaluated again and the final analysis ends up with the optimal solution. The Final Analysis is a branch and bound search in the space of partial solutions, each node records the spare row and column assignments.

## 4.RESULT AND SIMULATION OUTPUT

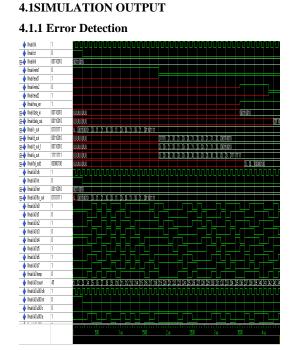

#### Fig 4.1 Simulation Output for Error Detection

The MODELSIM simulation output of error detection as shown in Fig.5.1. First the input data to write give write-'1' to enable. After to read the input data give read-'1'to enable and write-'0'to disable. In the three data the last bit is error occurs, the fault data bits are shown in d-out-f and the input data bits are shown in d-out.

Error

4.1.2

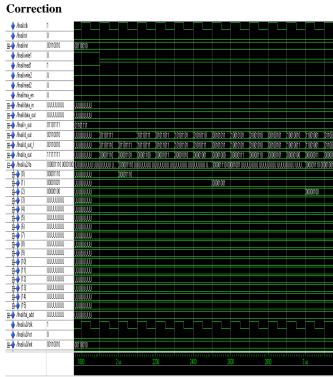

Fig 4.2 Simulation Output for Error Correction

The MODELSIM simulation output of error correction as shown in Fig.5.2. The fault data addresses are store in fault/u2/fa. Using the spare wires to correct the error bits and also again to read and write the data using give to write2-'0' and read2-'1'. Finally, to check the error correction output data bits shown in d-out.

#### **4.2 POWER CONSUMPTION**

## International conference on Advanced Techniques in Communication Networking and Automation

| 4.2.1                                                                   |                              | Existing            |              |              |                       |            |

|-------------------------------------------------------------------------|------------------------------|---------------------|--------------|--------------|-----------------------|------------|

| Power                                                                   |                              |                     |              |              |                       |            |

| Xilinx XPower - [final]                                                 |                              |                     |              |              |                       |            |

| ੇਸਿੰe Edit Wew Tools Window Help<br>ਡਿਊਊ ਪਿਆ ਦੇ ਨਾ - ਸੋਸ਼ੀ ਨਿੰਿ ਯੂ j ਕਿ | <b>1</b> 0                   |                     |              |              |                       |            |

| - M   1 + 1 → 10   ≤ 0 T   →                                            | 1                            |                     |              |              |                       |            |

| Voltage (V) Current (mA Power (mW                                       |                              | Power su            | IURALY:      |              | línð                  | PinW       |

| fccint 1.8                                                              |                              | Total estimated por |              |              | Address of the second | 373        |

| Dynamic 188.31 338.96                                                   |                              |                     |              |              |                       |            |

| Quiescent 15.00 27.00                                                   |                              | Feciat              | 1.807:       |              | 203                   | 366        |

| /cco33 3.3                                                              |                              | Vice 33             | 3.30V:       |              | 2                     | 7          |

| Dynamic 0.00 0.00<br>Quiescent 2.00 6.60                                |                              |                     |              |              |                       |            |

| ullescen: 2.00 6.60<br>otal Powe 372.56                                 |                              | Clacks:             |              |              |                       | 324        |

| tatup Cune 500.00                                                       |                              | Inputs:             |              |              |                       | B          |

| attery Capacity (mA Hours) 0.00                                         |                              | Leg                 |              |              | 1                     |            |

| attery Life (Hours) 0.00                                                |                              | Outp                |              |              |                       |            |

|                                                                         |                              | Fee                 |              |              | 1                     |            |

|                                                                         |                              | Sign                |              |              | 1                     | 1          |

|                                                                         |                              |                     |              |              |                       |            |

|                                                                         |                              | Quiescent V         | cint 1.80V:  |              | В                     | 27         |

|                                                                         |                              | Ouiescent W         |              |              | 2                     | 7          |

| Summary Power S Current S Thermal                                       | _                            |                     |              |              |                       |            |

| Data Views                                                              |                              |                     | mal surmary: |              |                       |            |

| E Clocks                                                                |                              | junction temperate  | UR:          |              | 31C                   |            |

| e 🔄 Looks                                                               | Andrient temp:               |                     |              |              | 25C                   |            |

| E Cojic                                                                 |                              | Case temp:          |              |              |                       | 30C        |

| e 🔄 Outputs<br>e 🔄 Signals                                              |                              |                     | Theta J-A:   |              |                       | 17C/W      |

| Repart Views Power Report (HTML) Power Report                           |                              |                     |              |              |                       |            |

|                                                                         | Invalid Program Mode Invalid |                     |              |              |                       |            |

|                                                                         |                              | ecoupling Network S |              |              | Cap Range (uF)        |            |

|                                                                         |                              | Capacitor Recommen  |              |              |                       |            |

|                                                                         |                              | Total for Verin     | t            |              |                       |            |

|                                                                         |                              |                     |              |              | 470.0-1000.0          |            |

|                                                                         |                              |                     |              |              | 4.70-10.00            |            |

|                                                                         |                              |                     |              |              | 0.470-2.200           |            |

|                                                                         |                              |                     |              |              | 0.0470-0.2200         |            |

|                                                                         |                              |                     |              |              | 0.0100.00400          |            |

| *                                                                       |                              |                     |              | NUM          | 2s600efg676-7         |            |

| 🖌 start 🔹 📦 Inbox (965) 🔁 4 Winds                                       | e                            | NodelSim S          | 3 WordPad    | - 🗟 Document | 1 🚦 Xiirox XPow       | <b>C D</b> |

| S.NO | PROCESS  | POWER CONSUMPTION<br>(mW) |  |  |

|------|----------|---------------------------|--|--|

| 1.   | Existing | 373                       |  |  |

| 2.   | Proposed | 113                       |  |  |

#### CONCLUSION

In proposed an on-chip infrastructure for repair analysis with the optimal repair rate for word oriented memories.As part of repair analyzer, and also developed a novel combinatorial circuit formulation allows to use the parallel prefix algorithm; it can be configured in various ways to meet area and test time requirements. The built in self repair analyzer used to detect and correct the errors in word oriented memories with single test. The linear feedback shift register used to count the next state and also requires high transitions in BIST architecture, required 373mW power. This system proposed methods using the bit swapping linear feedback shift register to reduce both the transition and the power consumption as 113mW. This has been achieved by using low-cost on-chip selection mechanisms, which are instrumental in very accurate and power reduction identification of failing rows, columns, and word oriented memories.

### **6.1FUTURE WORK**

The content addressable memory (CAM) is used to identify the fault address and it can be store in Must-Repair-Analyzer (MRA). The function of CAM is to search the fault address in one by one in MRA; it requires high searching time to identify the fault address. In future work by using Pre <sup>1</sup>/<sub>2</sub> computational-CAM is to identify the fault address easily, and also reduce the searching time. These modifications are implementing to the FPGA

kit.

Fig 5.3 Existing Power Consumption

The Xilinx Power Summary of Existing and Proposed System is as shown in Fig 5.3 and 5.4. Here before using the linear feedback shift register required high transition and 373mW power. By using Bit swapping –LFSR require low transition and also require only 113mW power.

#### 5.2.2 Proposed Power

Fig 5.4 Proposed Power Consumption 5.3 COMPARISON FOR OUTPUT POWER Table 5.1 Comparison Tablefor Power Consumption

#### APPENDIX port library ieee; (clk : in std\_logic; use ieee.std\_logic\_1164.all; : in std\_logic\_vector(7 downto 0); ad entity final is f.f1 : in std\_logic\_vector(7 downto 0); mra\_en : in std\_logic; port( clk,rst : in std\_logic; init : in std\_logic\_vector(7 downto 0); fa\_add : out std\_logic\_vector(7 downto 0) Write1 : in std\_logic; Read1 : in std\_logic; Write2 : in std\_logic; ); Read2 : in std\_logic; end component; mra\_en : in std\_logic; Data\_in : in std\_logic\_vector(7 downto 0); Data\_out : out std\_logic\_vector(7 component solver is downto 0); v\_out : inout std\_logic\_vector(7 downto 0); Clock : in std\_logic; port( D\_out : inout std\_logic\_vector(7 downto 0) Write : in std\_logic; Read : in std\_logic; f\_add : in std\_logic\_vector(7 end final; downto 0); Data\_in : in std\_logic\_vector(7 architecture str of final is downto 0); component bs\_lfsr is Data\_out : out std\_logic\_vector(7 port( clk,rst : in std\_logic; downto 0) init : in std\_logic\_vector(7 downto 0); lfsr\_out : out std\_logic\_vector(7 downto 0)); ); end component; end component; D\_out\_f : std\_logic\_vector(7 downto 0); component memory is signal signal a\_out : std\_logic\_vector(7 downto 0); Clock : in std\_logic; signal fal\_add : std\_logic\_vector(7 downto 0); Write : in std\_logic; Read : in std\_logic; begin Data\_in : in std\_logic\_vector(7 downto 0); u0:bs\_lfsr port map(clk,rst,init,v\_out); Data\_out: out std\_logic\_vector(7 u1:memory downto 0): map(clk,Write1,read1,v\_out,D\_out\_f,a\_out); Data\_out\_f: out std\_logic\_vector(7 u2:mra downto 0); map(clk,a\_out,D\_out\_f,mra\_en,fal\_add); add\_out : out std\_logic\_vector(7 downto uu3:solver map(clk,Write2,read2,fal\_add,Data\_in,Data\_out);

end component;

);

port(

end str;

component mra is

0)

);

port

port

port

## International conference on Advanced Techniques in Communication Networking and Automation

#### REFERENCES

W. Jeong, J. Lee, T. Han, K. Lee, and S. Kang, "An advanced BIRA for memories with an optimal repair rate and fast analysis speed by using a branch analyzer," IEEE Trans. Comput.-Aided Design Integr. CircuitsSyst., vol. 29, no. 12, pp. 2014–2026, Dec. 2016.

W. Jeong, I. Kang, K. Jin, and S. Kang, "A fast built-in redundancyanalysis for memorieswith optimal repair rate using a line-based searchtree," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 17, no.12, pp. 1665–1678, Dec. 2015.

P. Oehler, S. Hellebrand, and H.-J. Wunderlich, "Analyzing test and repair times for 2D integrated memory built-in test and repair," in Proc.Design Diag. Electron. Circuits Syst., 2014, pp. 1–6.

C.-T. Huang, C.-F. Wu, J.-F. Li, and C.-W. Wu, "Built-in redundancyanalysis formemory yield improvement," IEEE Trans. Reliab., vol. 52,no. 4, pp. 386–399, Dec. 2013.

S.-Y. Kuo andW. Fuchs, "Efficient spare allocation for learnays," IEEE Design Test Comput., vol. 4, no. 1, pp. 24–31, Feb. 1987.C.-T. Huang, C.-F. Wu, J.-F. Li, and C.-W. Wu, "Built-in redundancyanalysis formemory yield improvement," IEEE Trans. Reliab., vol. 52,no. 4, pp. 386–399, Dec. 2003.

X. Du and W.-T. Cheng, "At-speed builtin self-repair analyzer toembedded wordoriented memories," in Proc. Int. Conf. VLSI Design,2004, pp. 895–900.

B. Fitzgerald and E. Thoma, "Circuit implementation of fusible redundant addresses on RAMs for productivity enhancement," IBM J. Res.Develop., vol. 24, no. 3, pp. 291–298, 1980.